# **Annual Flash Controller Update**

David McIntyre

DSMcIntyreConsulting@gmail.com

Text **FMS** to (408) 772-7044

### **Overview**

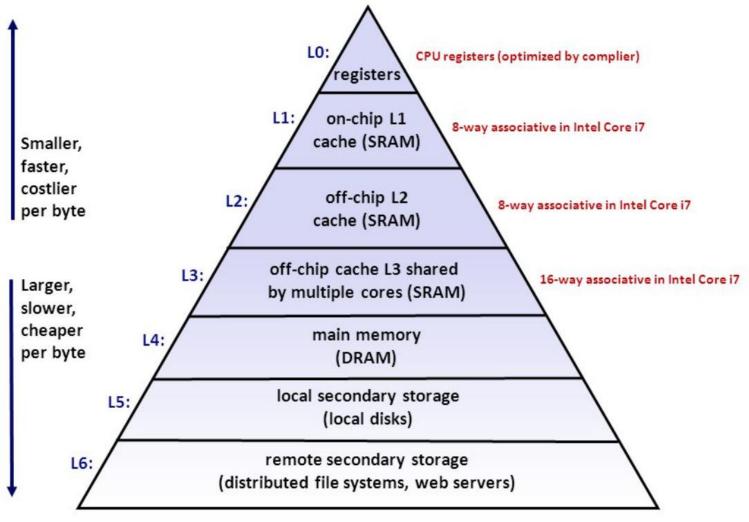

Data Center Drivers

Memory Hierarchy Drivers

Current Flash Controller Challenges

Supporting Technologies

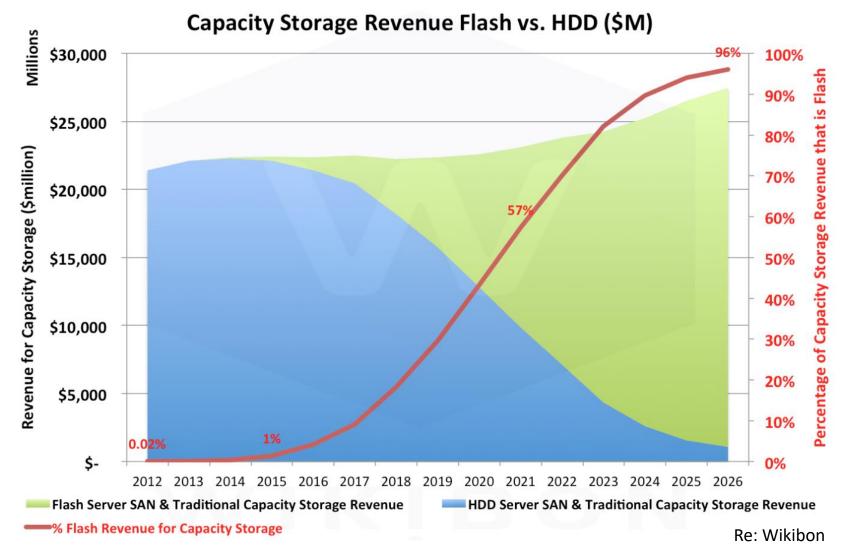

### **Data Center Trends**

- Hyper Converged Infrastructure

- Integrated Compute/Storage/Networking

- Massive interconnectivity

- Good for Exchange, Oracle, SQL databases

- Software managed virtualized resources

### Hyper Scale

- Independent scaling of compute and storage resources

- Good for elastic workloads, e.g. Hadoop, NoSQL

- Also software managed

### **Data Center Trends**

#### Storage

- Convergence of RAM/cache and SCM.

- All flash and hybrid arrays

- Persistent memory cache

### Compute

GPU, TPU and FPGA accelerators

### Networking

• Low latency, high performance RDMA networks

### Hybrid Cloud

- For lease and on premises-equipment

- Deployment Options, e.g. OpenStack and Docker

# **Hyperscaler Priority**

### Hyperscale in 2020

| By 2020, Hyperscale Data Centers Will House: |                                                       | Today:                 |

|----------------------------------------------|-------------------------------------------------------|------------------------|

| 47%                                          | of all data center servers                            | 21%                    |

| 68%                                          | of all data center processing power                   | 39%                    |

| 57%                                          | of all data stored in data centers                    | 49%                    |

| 53%                                          | of all data center traffic                            | 34%                    |

| dialo                                        | © 2016 Cisco and/or its affiliates. All rights reserv | ed, Cisco Confidential |

Flash controllers must support hyperscale requirements (latency, performance/watt, endurance, reliability)

Flash Memory Summit 2018 Santa Clara, CA

DS McIntyre Consulting LLC

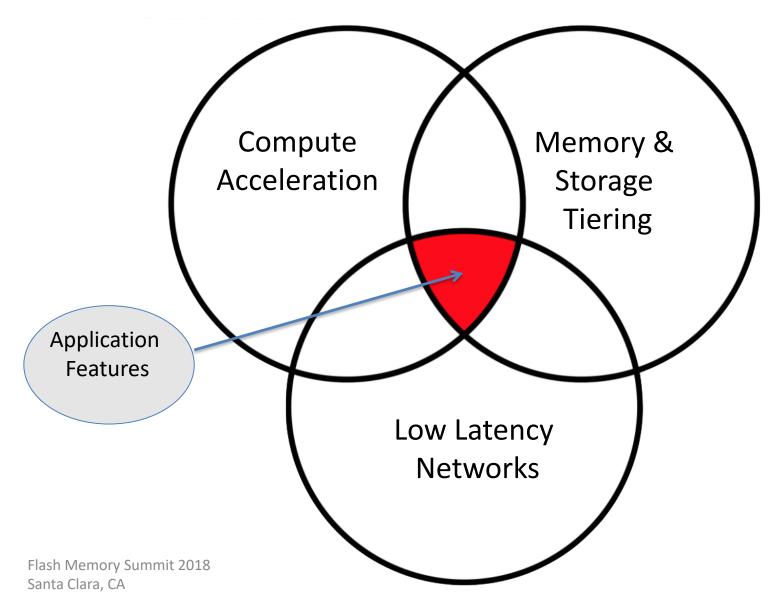

### **Supporting Infrastructure**

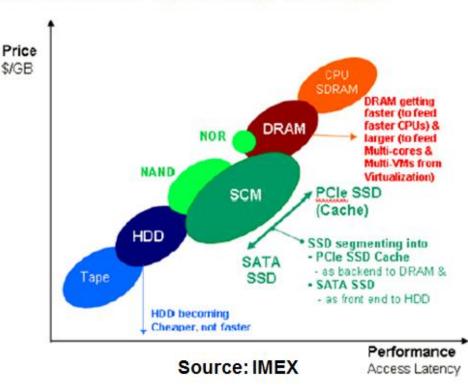

# **Memory and Storage Tiering**

Flash Memory Summit 2018 Santa Clara, CA

# **Changing of the Guard**

# **Flash System Challenges**

#### Price/Performance Gaps in Storage Technologies

- Error correction costs increasing

- Endurance limits

- Slow write speeds continue

- IO bottlenecking

- Emerging NV technologies (MRAM, PCM, RRAM)

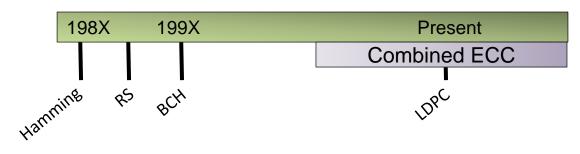

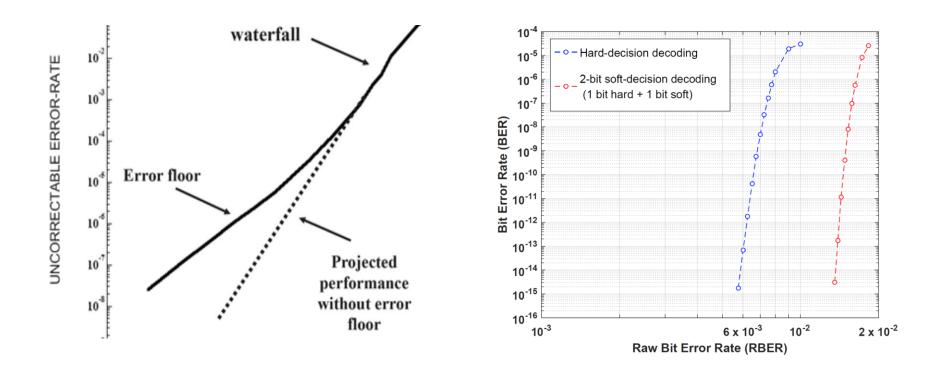

### **Error Correction Overview**

#### **Driving Factors for New ECC**

- Increasing Bit errors in NAND Flash

- Soft error occurrences

- Decrease in write cycles

- RS, BCH overhead for data and spare area

- Increase use of Metadata in file systems

- Correction Overhead

- Gate count

- Requirement for no data loss

#### **Comparing ECC Solutions**

| Features      | BCH | LDPC   |

|---------------|-----|--------|

| Gate<br>Count | Low | Mid    |

| Latency       | Low | Medium |

| Tuneablity    | low | high   |

| Soft Data     | No  | Yes    |

### **Example Codelucida LDPC**

#### Efficient ECC with NVMe Performance for 3D NAND TLC/QLC

# Flash Memory Summit Flash Controller Support

| IP                 | ю          | Speed    | Logic Density | Comments                                              |

|--------------------|------------|----------|---------------|-------------------------------------------------------|

| ONFI 4.1           | 40 pins/ch | 400 MTps | 5KLE/ch       | NAND flash control, wear leveling, garbage collection |

| Toggle<br>Mode 2.x | 40 pins/ch | 400 MTps | 5KLE/ch       | Same                                                  |

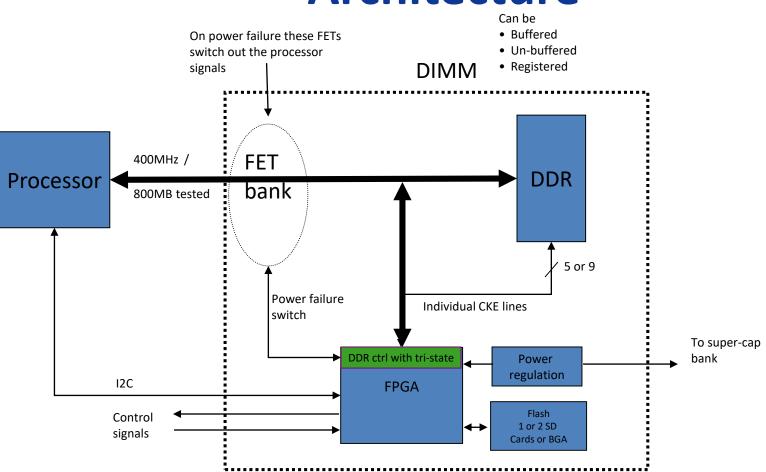

| DDR4               |            | 3.2Gbps  | 10KLE         | Flash control modes available for NVDIMM              |

| PCM                |            |          | 5KLE          | PCM- Pending production \$                            |

| MRAM               |            |          | 5KLE          | MRAM- Persistent memory<br>controller                 |

| BCH                |            |          | <10KLE        | Reference design                                      |

| PCIe               | G4x8       | 128Gbps  | HIP           | Flash Cache                                           |

### **Persistent Friend or Foe**

- Intel/Micron Xpoint Claimed Attributes vs. NAND

- Performance (10X)

- Endurance (1000X)

- Latency (1/1000X)

- Byte addressable

- Est Cost (2X+)

- Opportunity for NAND to support load/store-driven data center applications (NVDIMM-F and NVDIMM-P)

### **Flash Controller Challenges: Now**

#### Host Interface IO

- Gen Z, CCIX, OpenCAPI

- PCle Gen 4

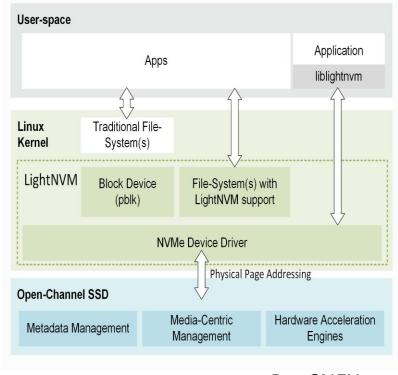

- Open Channel

#### Application Requirements

- Deterministic latencies

- Load/Store vs Block

- Performance

- Endurance

#### Hybrid Control

- 3D NAND, 2D NAND

- Cache: 3DXpoint, MRAM

Flash Memory Summit 2012 Santa Clara, CA Flash Memory Summit 2017 Santa Clara, CA

### **Coherent Networks Roadmap**

### Cache coherency will continue to expand into SCM into SSD caches

| <u>NE</u> | R         |                              | SoC ATTACH      |                 | FAR         |

|-----------|-----------|------------------------------|-----------------|-----------------|-------------|

| HBM       | DDR       | Accelerator / Local SCM      | Chassis SCM     | Rack Pooled SCM | Messaging   |

|           |           | PCIe Phy CCIX                | Future Spec     | Rev             |             |

|           | r -<br>18 | 02.3 short and long haul Phy | Gen-Z           |                 |             |

|           | -<br>  8  | <sup>02.3 Phy</sup> OpenCAPI | Future Spec Rev |                 |             |

|           |           |                              |                 | I               | Re: OFA.org |

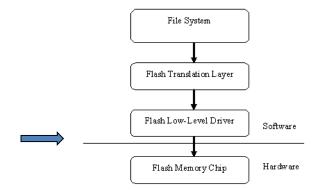

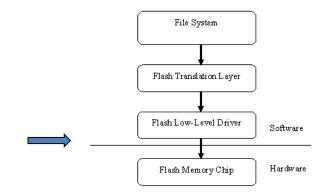

### NVDIMM Controller Architecture

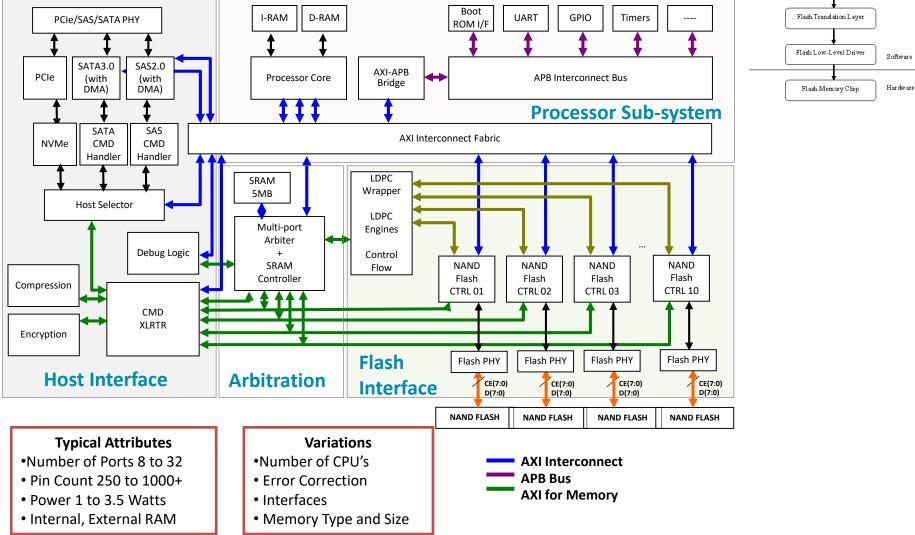

### Typical SSD Controller Architecture

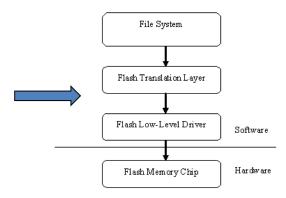

File System

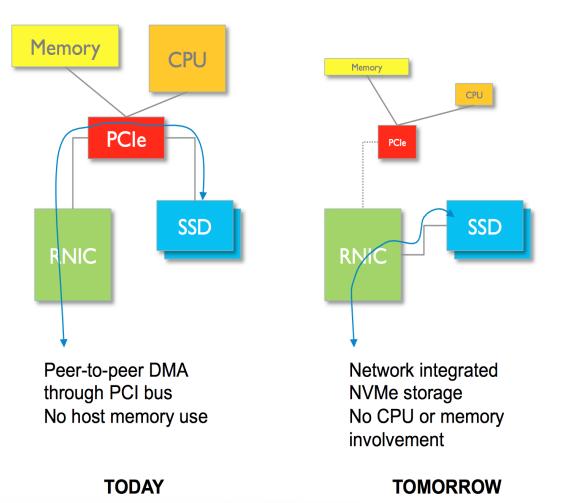

### NVMe Roadmap- a NVMeF Precursor

SNIA

DMA to/from host memory CPU handles command transfer

YESTERDAY

### **NVMeF- Key Value Points**

OpenFabricsAlliance.org

#### **Encapsulated protocol transmitted over fabrics**

RDMA (iWARP, RoCE) FC, Infiniband, L1 Tunneling

The goal is to enable next-gen technologies to deliver a 4KB I/O in less than 10 $\mu s$  - about one thousandth of the latency of a 7200 RPM SATA drive

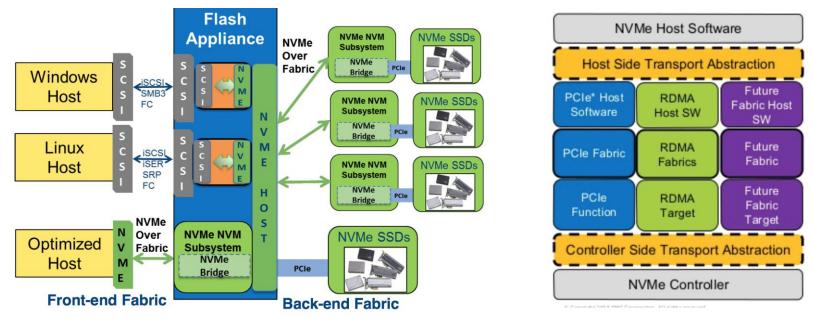

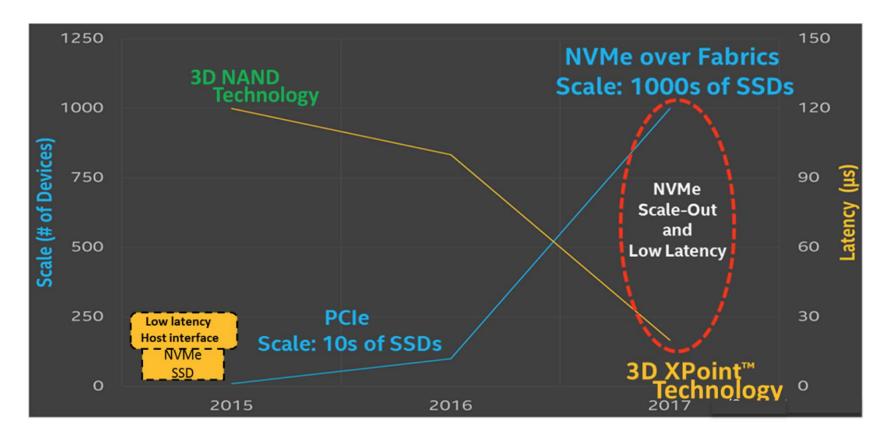

### **SSD Scale Out over Fabrics**

NVMeF breaks through local NVMe barrier and supports low latency

### Flosh Memory Summit Open Channel Pros and Challenges

- I/O Isolation and Determinism

- Software managed resources

- Application-centric

- Linux kernel support required

- Vendor-specific attributes

Re: CNEX

### **Differentiation Paradox**

- Hyperscaler standardization

- Vendor competitive selling features

- >Application requirements

- I/O

- Power Consumption

- Capacity

- Latency

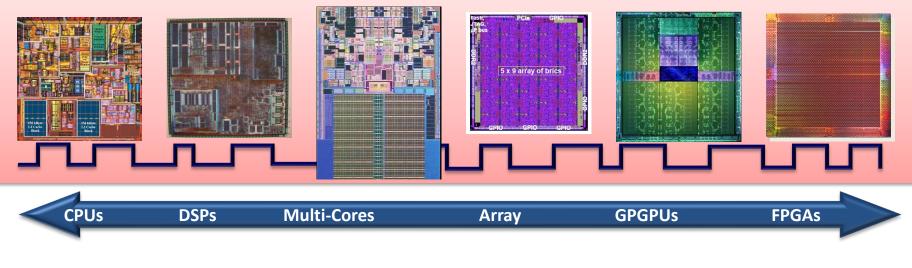

# **Controller Options**

#### Technology scaling favors programmability and parallelism

Single Cores

Multi-Cores Coarse-Grained CPUs and DSPs Coarse-Grained Massively Parallel Processor Arrays

Fine-Grained Massively Parallel Arrays

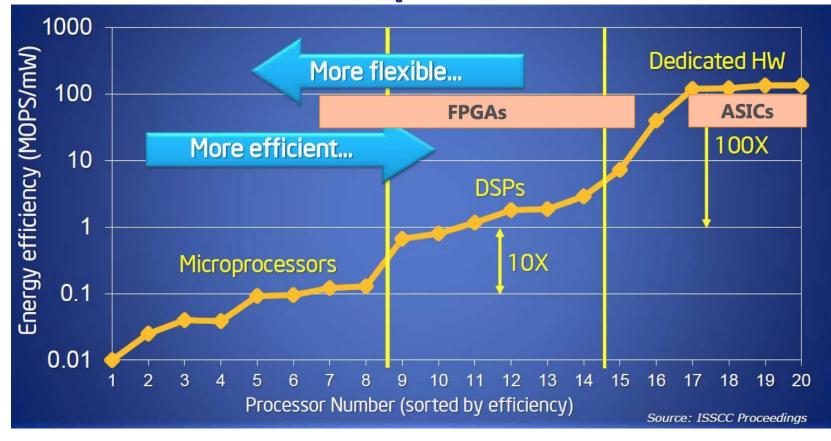

### Flash Controller Technology Options

- Data center metric is performance/watt

- Performance, power efficiency and flexibility is required to support data center applications

# Flash Memory Summit Technology Comparison

| Technology | Pros                                                                 | Cons                                                                                                      |

|------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| CPU        | Well established products                                            | <ul> <li>Limited cores for<br/>parallel processing</li> <li>Power consumption</li> </ul>                  |

| FPGA       | Heterogeneous parallel processing<br>Performance/Watt<br>Flexibility | <ul> <li>Rudimentary<br/>development<br/>environment</li> <li>Inefficient per unit<br/>costing</li> </ul> |

| GPU        | Same task parallel processing<br>Developer ecosystem                 | <ul><li>Power consumption</li><li>Leading variable<br/>types</li></ul>                                    |

| ASIC       | Highest Performance                                                  | <ul> <li>High NRE</li> <li>Custom design</li> </ul>                                                       |

| ASSP       | Custom Performance                                                   | Limited functionality                                                                                     |

### Summary

- Flash Control has extended into tiered subsystem management

- Caching has extended into SCM, necessitating hybrid control

- IO interfaces need to support fabric

- Advancing geometries and process technologies require more and advanced error correction

- Hyperscaler applications demand load/store performance with deterministic latency

# **Annual Flash Controller Update**

David McIntyre

DSMcIntyreConsulting@gmail.com

Text **FMS** to (408) 772-7044

### Flash Controller Challenges: Then

#### Emerging memory types

- ONFI 4.0, Toggle Mode 2.x

- PCM, MRAM

- DDR4

#### Controller Performance Options

- Write back cache, queuing, interleaving, striping

#### ECC levels

- BCH, LDPC, Hybrid

- FTL location- Host or companion

- Data transfer interface support

- PCI Express, SAS/SATA, FC, IB

### Flash Controller Challenges: Now

#### I/O Performance

- Interchip coherency

- Host Communications

- Network

- Latency

- HPC network latencies

- Density

- 3D, HBM2

- Heterogeneous flash memory types

- Reliability and Endurance