# Emerging Challenges in NAND Flash Technology

#### Seaung Suk Lee

Vice President Flash Product Planning Group Hynix Semiconductor Inc.

NAND Flash Market Overview

Technology Scaling Trend & Forecast

Technology Scaling Limitation & Hurdle

Future Technology Development Direction

### NAND Flash Market Overview

- Technology Scaling Trend & Forecast

- Technology Scaling Limitation & Hurdle

- Future Technology Development Direction

# Market Revenue Forecasting

### Expect continuous NAND market growth; \$29.1B in 2014

[Source; WSTS2011]

Good memory

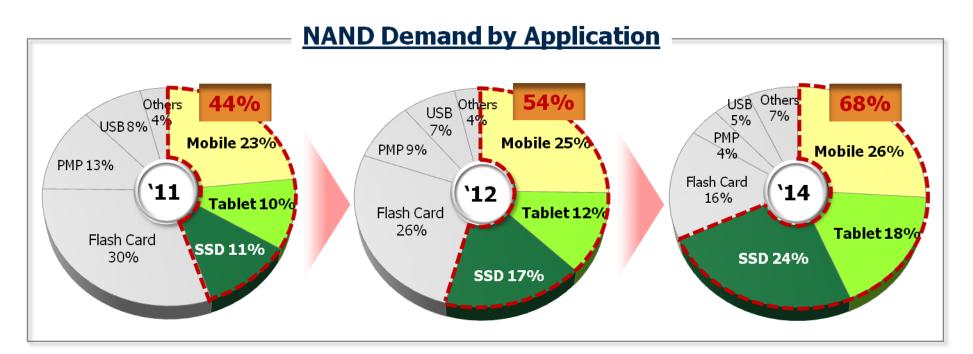

# Prospective Application Trend

### Mobile, Tablet, SSD dominate NAND demand in 2011~2014

[Source; Hynix Marketing 2011]

◆ Low Cost✓ Bit growth

High Performance

+ Controller SW solution

High Reliability

+ Controller SW solution

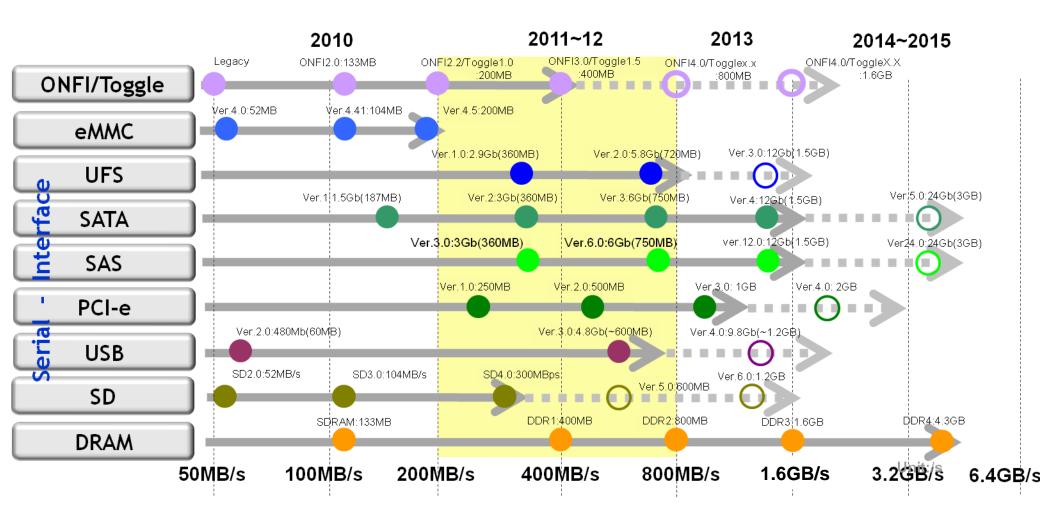

# Standard Interface Trend; Performance

# Presentation Agenda

NAND Flash Market Overview

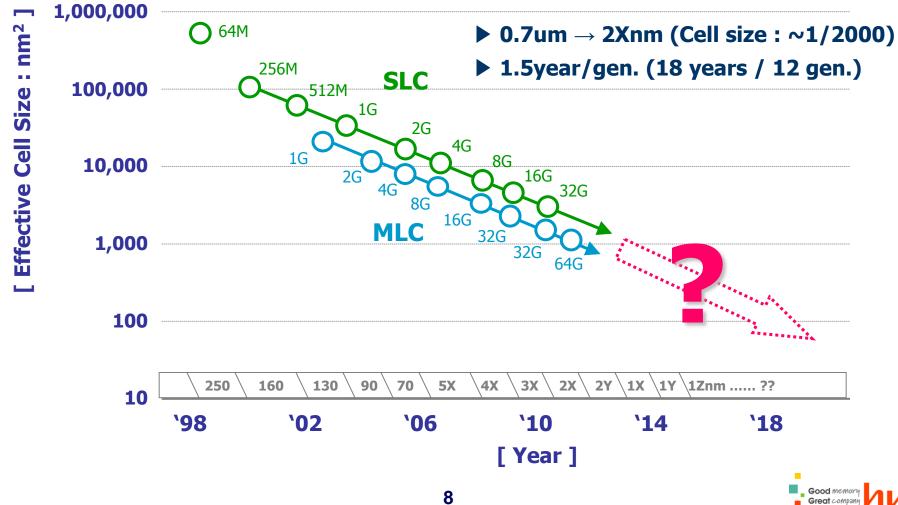

### Technology Scaling Trend & Forecast

Technology Scaling Limitation & Hurdle

Future Technology Development Direction

#### hynix **Further Scaling Solution?**

#### Conventional FG NAND cell has been scaled down over 18 years.

# Presentation Agenda

#### NAND Flash Market Overview

#### Technology Scaling Trend & Forecast

### Technology Scaling Limitation & Hurdle

#### Future Technology Development Direction

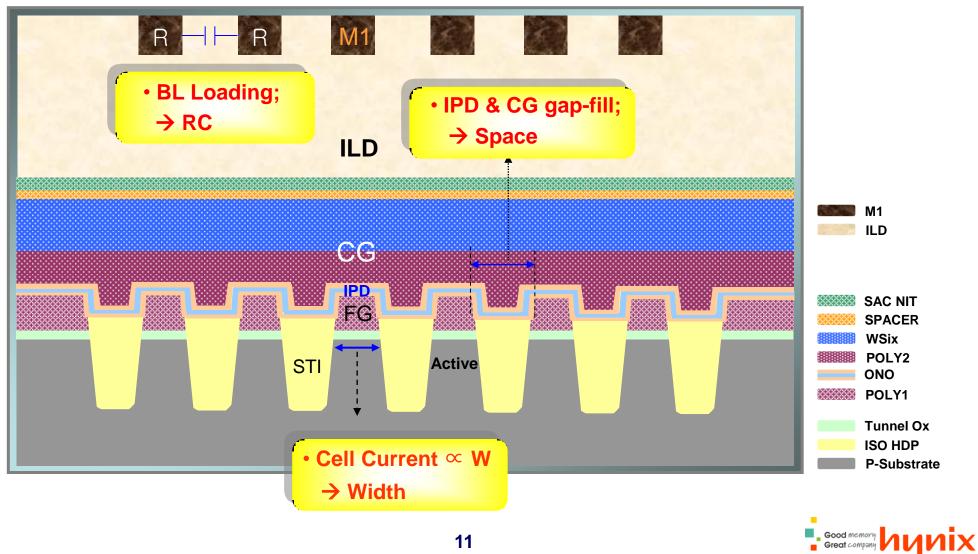

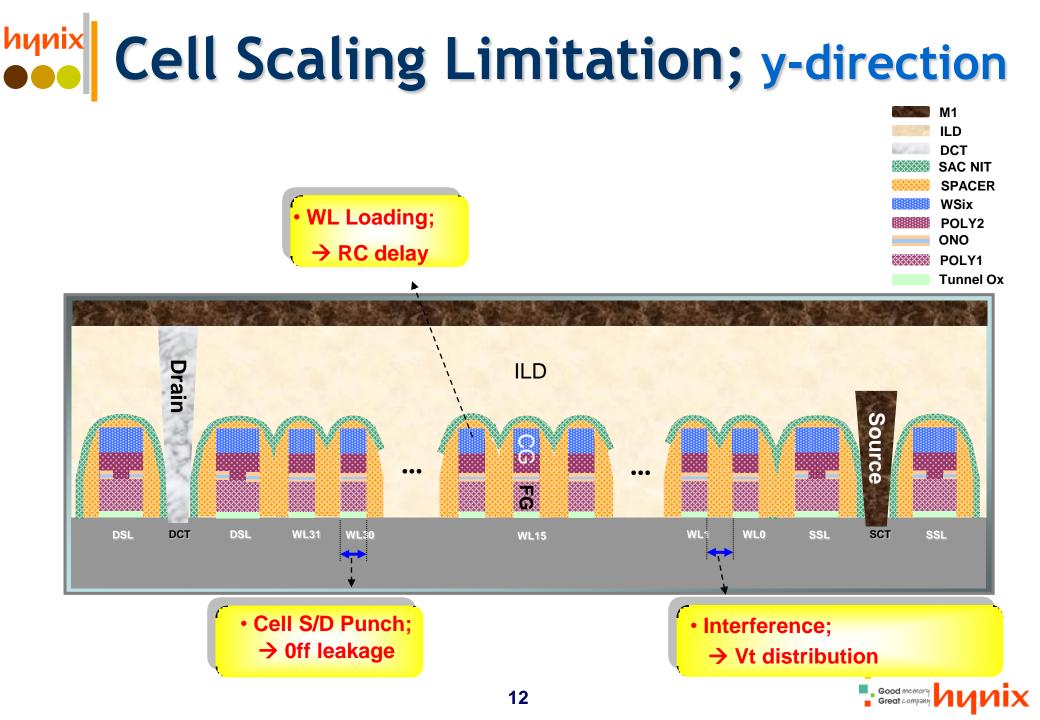

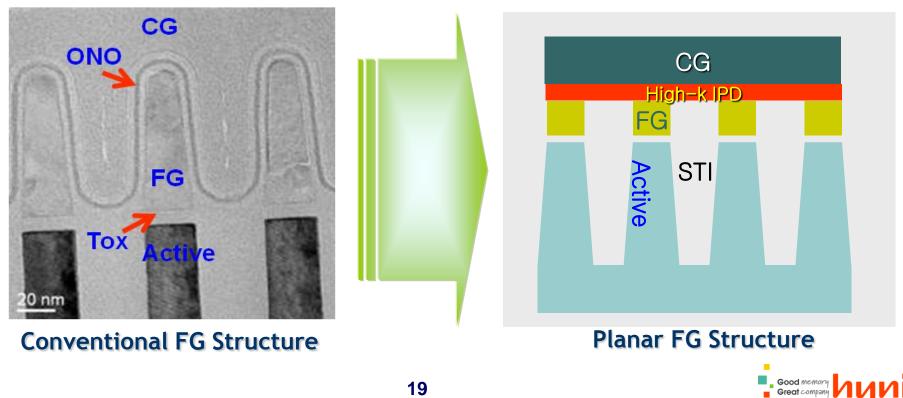

### Scaling Limitation of FG Cell

### Physical Limitation;

- ✓ Patterning

- ✓ Structure formation : FG, CG, IPD ...

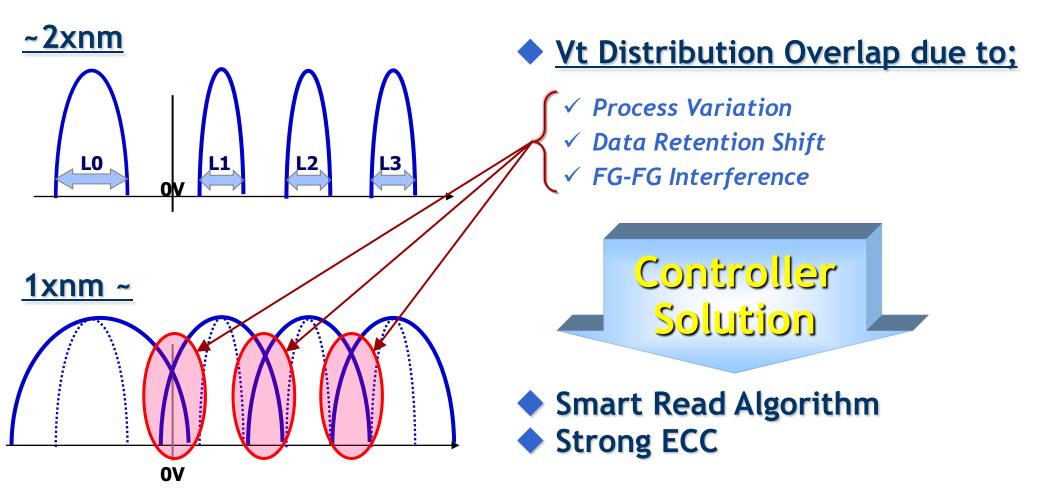

### Electrical Limitation;

- ✓ Interference

- Capacitive coupling ratio

- $\checkmark$  No. of electron in FG

- ✓ Dielectric leakage

#### **му**міх Cell Scaling Limitation; x-direction

#### ✓ ASA-FG Advanced Self-Aligned Floating Gate

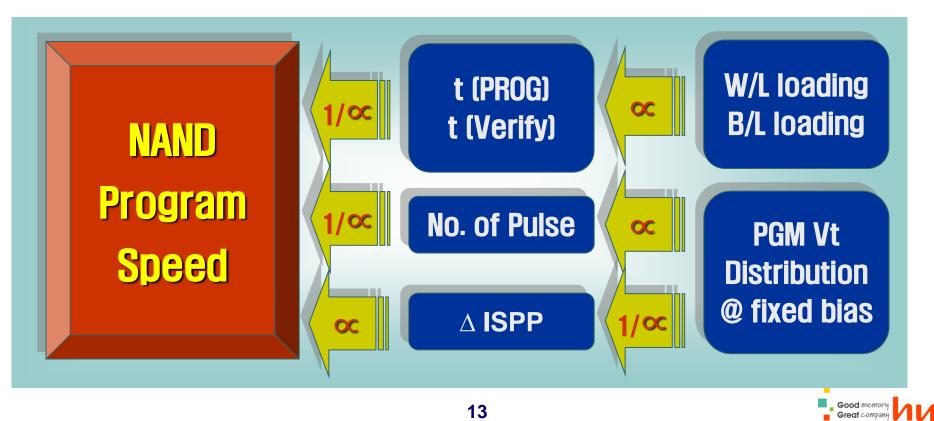

#### Program Speed = t (PROG + Verify) X N

- tPROG ; unit program & verify time

- N; no. of ISPP

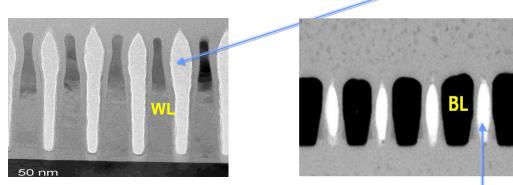

# WL & BL Loading Improvement

### WL Loading

- Material; Poly- Si  $\rightarrow$  CoSix  $\rightarrow$  W

- WL Space; Vertical Profile → Low-k dielectric → <u>Air Gap</u>

- Material;  $W \rightarrow Al \rightarrow Cu$

- BL Space; Vertical Profile  $\rightarrow$  Low-k dielectric  $\rightarrow$  Air Gap

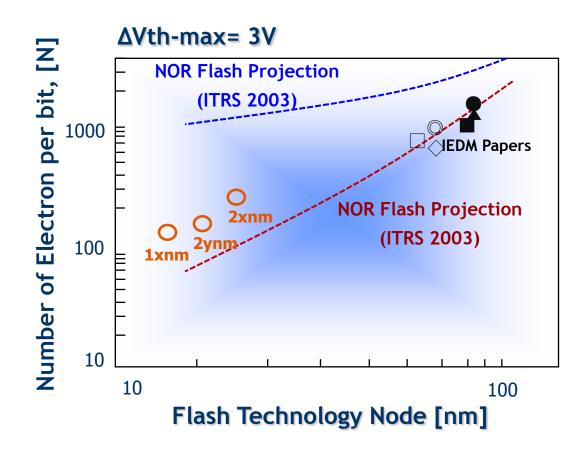

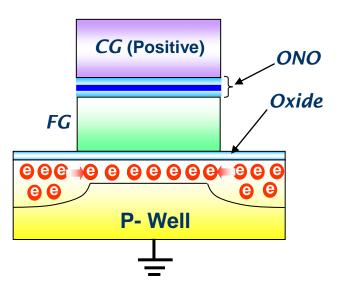

# No. of stored electrons in FG

#### **Program Operation**

### Read Window Margin Solution

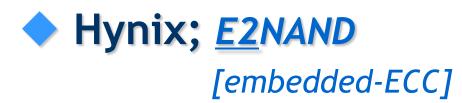

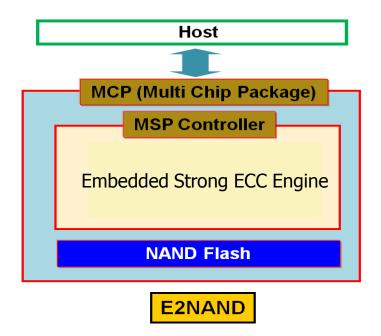

# Enhanced Solution Products

# Presentation Agenda

#### NAND Flash Market Overview

#### Technology Scaling Trend & Forecast

Technology Scaling Limitation & Hurdle

### Future Technology Development Direction

#### һүиіх Planar FG with High-k IPD

### CG Gap-filling & Interference Thin FG structure with High-k IPD ✓ FG vertical scaling

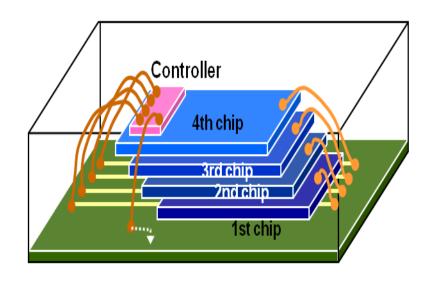

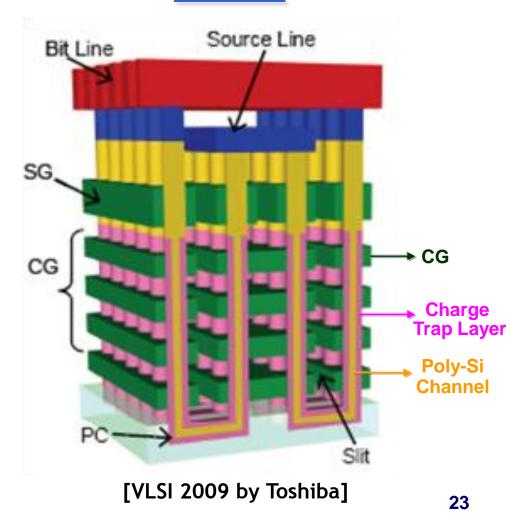

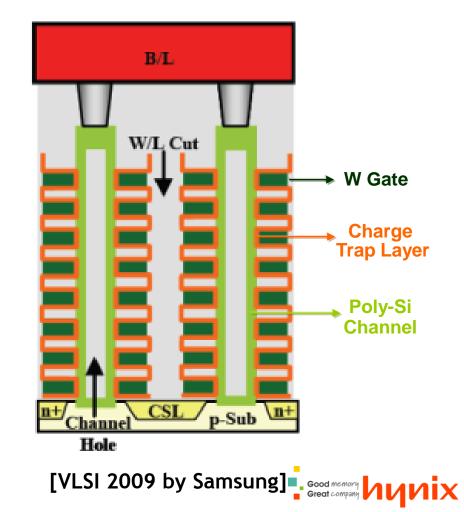

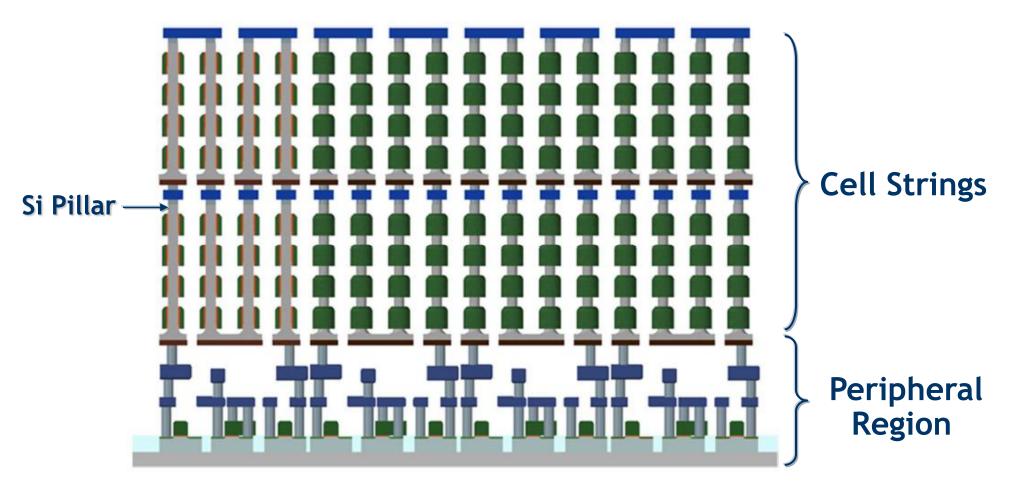

#### Stacked 3D with SONOS structure

#### Stacked 3D with FG structure

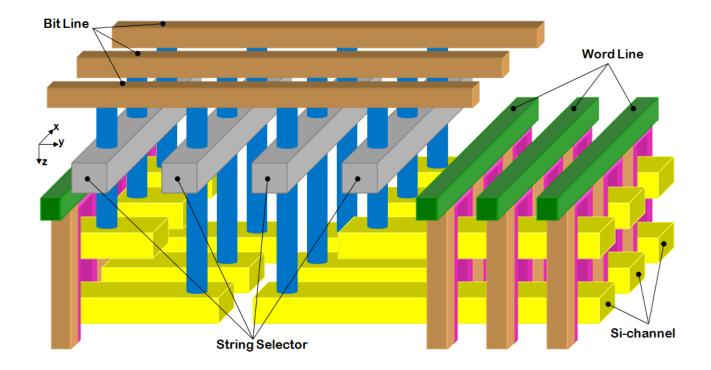

### Si Pillar 3D with wafer bonding technology

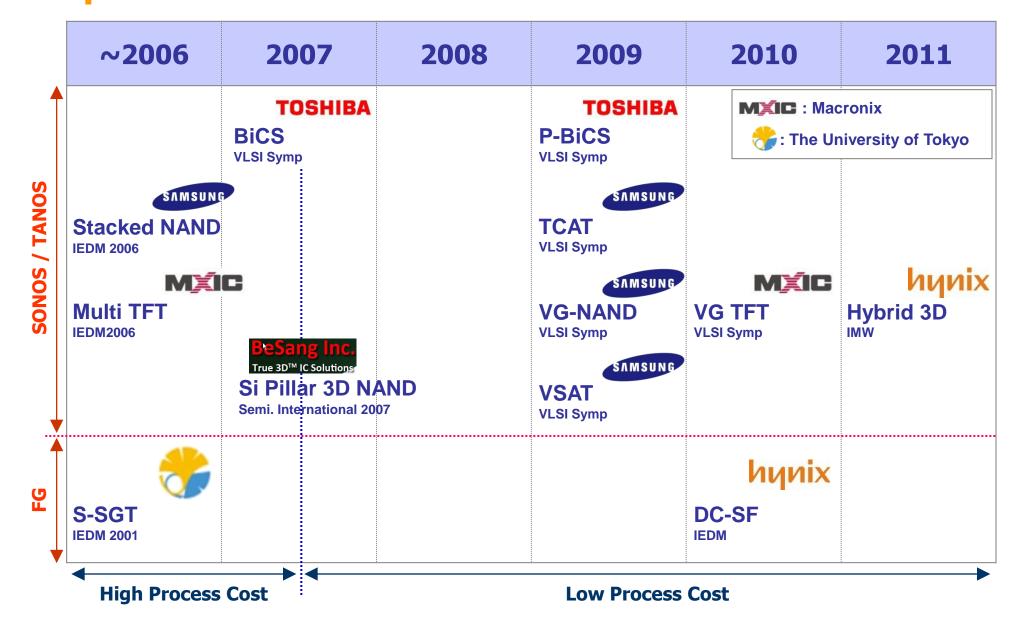

# History of 3D NAND Flash

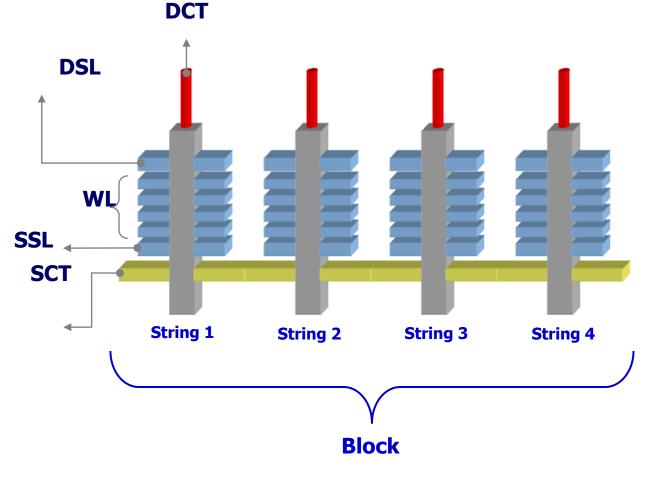

### **3D NAND Cell string**

**P-BiCS**

#### **Hybrid Stacked 3D**

3D Cell Structure with Horizontal Poly-Si Channel

[IMW 2011 by Hynix]

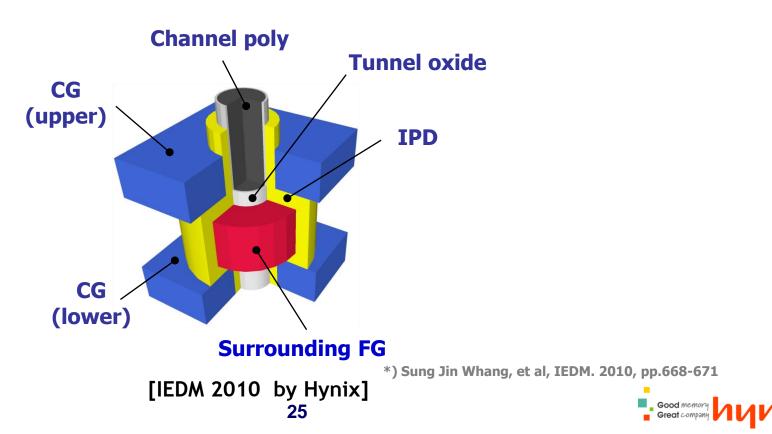

## Dual CG - Surrounding 3D FG Cell

New 3D Structure Concept with FG cell

Surrounding FG is controlled by two control gates.

Single cell

[Semi. International 2007 by BeSang Tech.]

# **Future Technology Analysis**

| Technology | Strong Points                     | Weak Points                               |

|------------|-----------------------------------|-------------------------------------------|

| Planar FG  | Friendly Structure                | High-k Dielectric Stability               |

| FG-3D      | Reliability<br>Small Interference | Scaling Limitation<br>Stacking Limitation |

| Stacked 3D | Low Cost<br>Small Interference    | New Materials<br>SONOS Reliability        |

| Si Pillar  | Approved Materials<br>Scalability | Wafer Bonding Cost<br>SONOS Reliability   |

# What are Decision Points ?

# Who is Winner at Post 1x or 1y nm ?

### Somebody will find a solution.

hynix Thank you!