A Complete System Approach to NAND in Computing

**Dean Klein**

Micron Technology, Inc.

©2010 Micron Technology, Inc. All rights reserved. Products are warranted only to meet Micron's production data sheet specifications. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Dates are estimates only. Drawings are not to scale. Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

### Issues with Storage (aka: Memory)

Performance: The Memory Wall

Power: Exabytes and Megawatts

Reliability: Redundancy and Resiliency

Scaling: Density and Cost

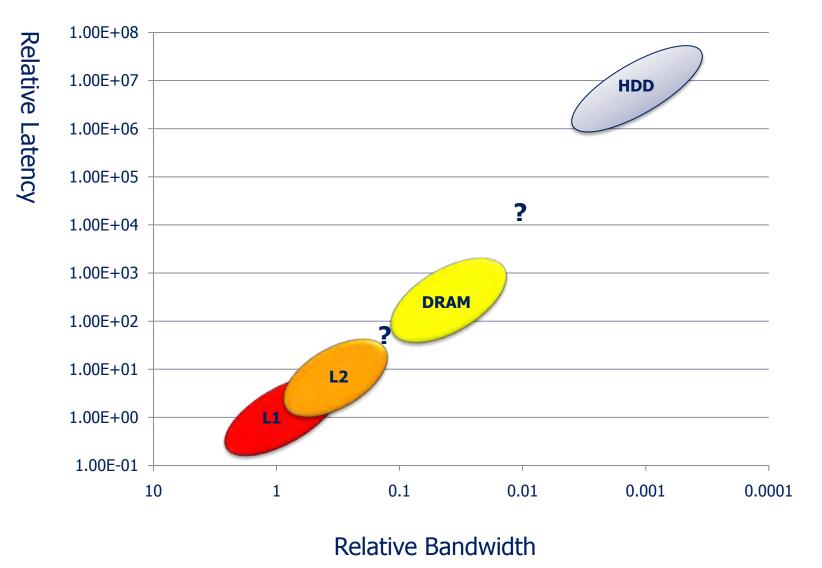

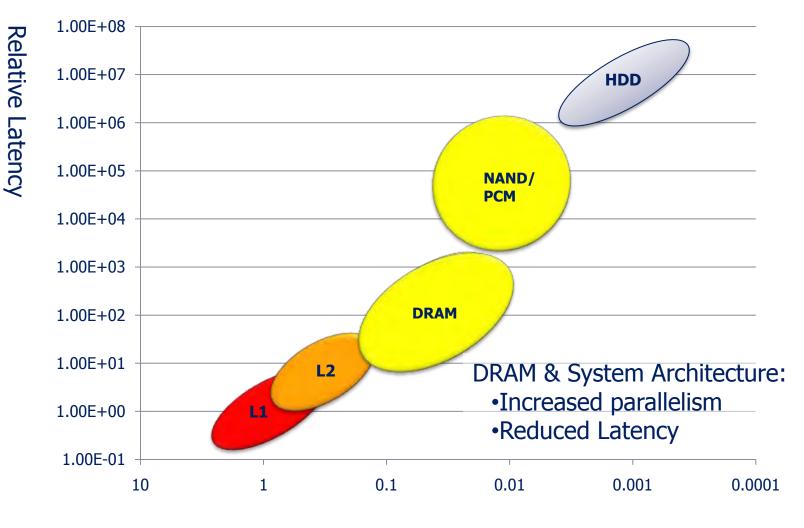

### Memory Hierarchy Gaps

©2010 Micron Technology, Inc.

3

Micron

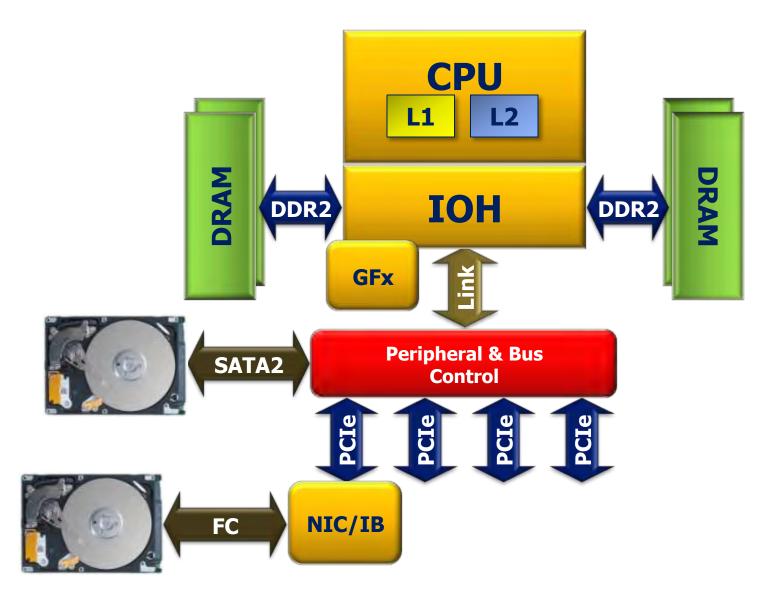

#### System Architecture

### System Architecture

# High Bandwidth: Up to 3.2 Gbps Power Consumption: 1.2V is 10-15%

- improvement over DDR3 & DDR3L

- High Density: 2Gb 16Gb; up to 8H (128Gb stack); single load

- DDR4 cost overhead appears better than previous 1<sup>st</sup> gen technologies

- **Power, density and bandwidth:** Optimized for HPC and servers

#### DDR4: Memory Architecture Improvement DDR4 is coming – High Bandwidth, Low Power, High Density

Major Advantages of DDR4:

#### Micron

٠

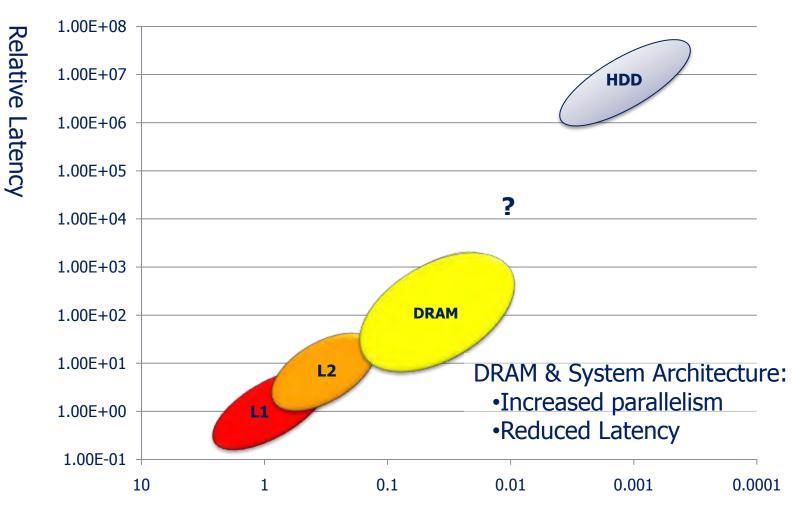

### Memory Hierarchy Gaps

#### **Relative Bandwidth**

### Memory Hierarchy Gaps

#### **Relative Bandwidth**

#### Requirements

- Low random latency:

- As the number of CPU cores (and thus the parallel tasks) increase the traffic becomes increasingly random.

- As the use of VM's increase the traffic becomes increasingly random.

- High endurance:

- Accepted DRAM endurance is >1E15 cycles.

- Accepted NAND endurance is <1E5 cycles or 3E3 cycles.</p>

- Intelligent management

## Closing the Storage to DRAM Gap

- Technical requirements:

- Low latency

- High endurance

- Symmetric read and write

- Block-based architecture

- Able to use existing interfaces

- Economic requirements:

- Lower cost/bit than DRAM

- Lower power than DRAM

#### **NAND Endurance**

- NAND Process and Design

- + Improved processes: new materials and structures

- Smaller geometries: fewer electrons and more interference

- SSD Architecture and Algorithms

- + Improved error handling and efficiency

- ++ NAND optimizations

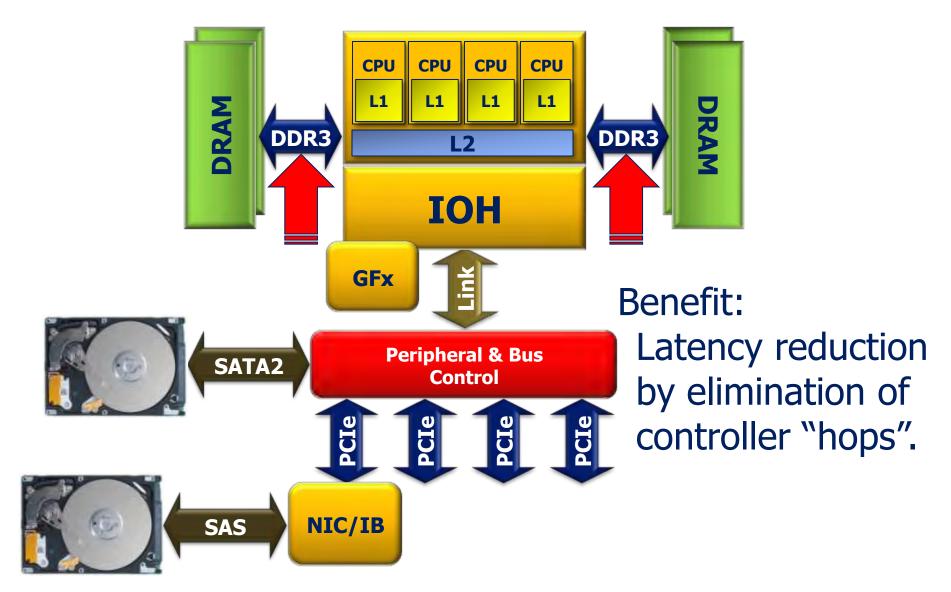

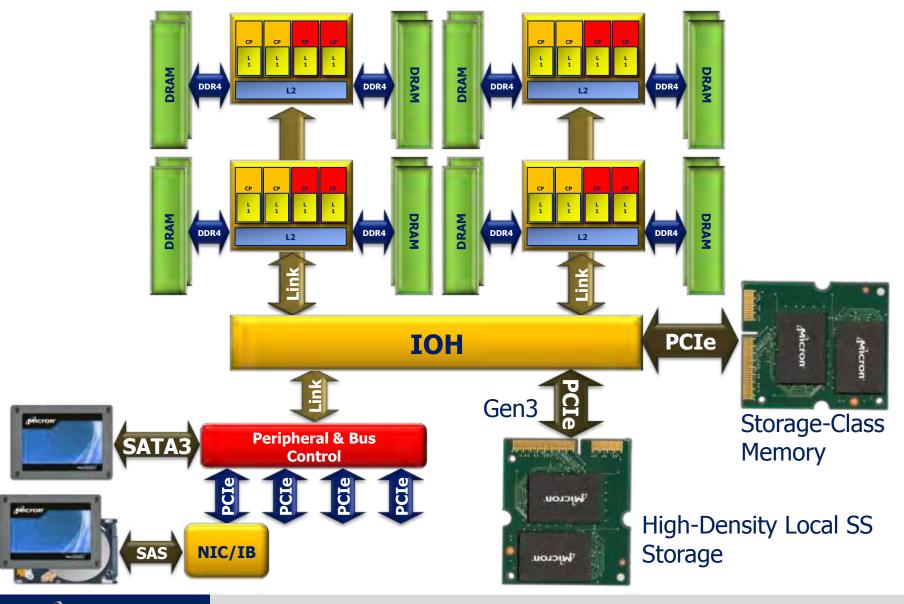

### Fast Forward: Future System Architecture

Micron

### Solid State Storage as the Ultimate Cache

- Pinnable, secure, high performance.

- System software can:

- Mitigate wear

- Allow graceful degradation

- Accelerate slower storage, both local and remote

- Fits with SSD today and PCM tomorrow.

- Can take advantage of lower latency, higher bandwidth connections.

- Optimized solution is integrated solution.

### The Holistic Approach to Storage

- The gap between CPU and main memory is being closed by architecture and DRAM advanced.

- The gap between DRAM and storage is widening.

- Increasing randomization of storage traffic demands a storage system with low random latency.

- Endurance requirements will dictate advanced NAND management, and must include system software as a part of the solution.

- NAND, and ultimately PCM, will close the storage gap.